文章编号:1001-2486(2011)02-0136-04

## 90 纳米 CMOS 双阱工艺下 STI 深度对电荷共享的影响\*

刘衡竹,刘凡宇,刘必慰,梁 斌 (国防科技大学 计算机学院,湖南 长沙 410073)

摘 要:基于 3 维 TCAD 器件模拟,研究了 90nm CMOS 双阱工艺下 STI 对电荷共享的影响。研究结果表明:增大 STI 深度能有效抑制 NMOS 电荷共享,且 550nm 为抑制电荷共享的有效深度,超过这个深度收集的电荷量几乎保持不变;而对于 PMOS,STI 深度的增加使电荷共享线性减小。这对于电荷共享加固具有重要指导意义。

关键词:电荷共享;单粒子效应;浅沟槽隔离(STI);双极效应

中图分类号:TP302 文献标识码:A

# Impact of STI Depth on Charge Sharing in 90nm CMOS Technology

LIU Heng-zhu , LIU Fan-yu , LIU Bi-wei , LIANG Bin

(College of Computer, National Univ. of Defense Technology, Changsha 410073, China)

**Abstract**: The dependence of various STI depths on charge sharing in 90nm dual well CMOS technology was investigated. TCAD simulation results show that increasing STI can restrain charge sharing of NMOS effectively, and 550nm is the effective depth for the prevention of charge diffusion, beyond which the collected charge almost keeps constant; for PMOS, charge sharing decreases linearly with the increment of STI depth. This conclusion is useful for irradiation-hardness.

Key words: charge sharing; SEE(single event effect); STI(shallow trench isolation); bipolar amplification effect

辐射环境中高能粒子引起半导体器件中产生的单粒子效应一直以来是受到广泛的关注。电荷共享是指单粒子效应产生的电荷同时被多个敏感节点收集<sup>[1]</sup>。电荷共享不仅能够导致存储单元发生多位翻转(Multi-Bit Upset, MBU),还能够导致组合电路中出现多个单粒子瞬态脉冲(Single Event Transient, SET),增加系统的软错误率,从而加大抗辐照加固设计的难度<sup>[2-5]</sup>。

目前电荷共享的加固主要通过版图技术来实现,如添加保护环,增大阱接触等,这些技术都增加了面积和功耗<sup>[6-7]</sup>。1984 年, Mikoshiba 等人提出用浅沟槽隔离(Shallow Trench Isolation, STI)来隔离深亚微米下的器件,以求去除"鸟嘴"带来的影响<sup>[8]</sup>。STI可以实现不同的纵横比,更窄的沟槽有利于更高的集成度,更深的沟槽可以实现更好的隔离。有研究证实,增大 STI 宽度,即增加器件的间距,可以有效减小电荷共享<sup>[9]</sup>,但 STI 深度对电荷共享的影响目前还没有研究。文献[9]通过数值模拟得出:深亚微米下电荷共享的机理主要包括漂移、扩散和双极放大效应。因此,通过研究不

同 STI 纵横比下电荷共享的变化趋势,有助于我们通过改善工艺,达到抑制电荷共享的目的。

### 1 模拟设置

#### 1.1 TCAD 模型校准

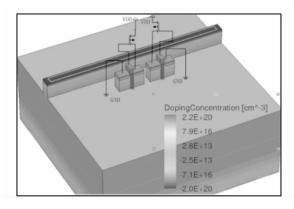

模拟中使用了两种电路结构:1)两个输入为"0"的反相器,两 NMOS 漏端相邻并采用 3 维器件模型,而两 PMOS 管采用电路模型,如图 1;2)两个输入为"1"的反相器,两 PMOS 漏端相邻并采用 3 维器件模型,而两 PMOS 管采用电路模型。这两种电路结构广泛地存在于各种电路设计中。器件模型的 P 阱杂质为硼,而 N 阱掺杂的为砷。通过调整漏轻掺杂(LDD)浓度、阈值电压( $V_T$ )注入和源漏掺杂的浓度,对 NMOS 和 PMOS 器件模型进行了工艺校准。该模型获得了与 SMIC 90nm Logic 1P9M Salicide CMOS 工艺相一致的电流电压特性曲线( $I_D - V_D$ ),如图 2 所示。

<sup>\*</sup> 收稿日期:2010-05-13

图 1 电荷共享模拟使用的 NMOS 管器件结构 Fig. 1 Device structure of two NMOS for charge sharing simulation

图 2 90nm CMOS 工艺校准获得的  $I_D - V_D$  曲线 Fig. 2  $I_D - V_D$  characteristic comparison between SPICE and TCAD modeling

-0.6

Vds/V (b) PMOS

-0.4

-0.2

0.0

-0.8

### 1.2 模拟建立

-120 **₽**i -1.2

-1.0

模拟中,我们采用 Synopsys 公司的 Sentaurus TCAD 构建了 3 维器件。NMOS 管和 PMOS 管的尺寸分别为  $W_n:L_n=200$ nm:90nm 和  $W_p:L_p=480$ nm:90nm。管子间距为 140nm,阱接触距 NMOS 和 PMOS 的距离为 280nm,使用 STI 隔离两个晶体管。工作电压设置为 1.2V。

重粒子轰击的 LET 值为 10MeV·cm²/mg,并在 轨迹上保持不变。粒子轨迹的深度和半径分别为 5μm 和 0.05μm。假定粒子轰击的位置为漏极的 中心,且垂直轰击器件结构的表面。这里将不讨 论有角度的粒子入射效应。 使用的物理模型包括:1) Fermi-Dirac 统计;2) 禁带变窄模型;3) 掺杂相关的 SRH 复合和 Auger 复合;4) 掺杂、电场和载流子浓度对迁移率的影响;5) 轰击的重粒子是采用 Gaussian 分布建模,且 Gaussian 时序分布有 0.25ps 的延迟;6) 流体动力学模型用来模拟载流子输运。其他的模型和参数为 Sentaurus TCAD 默认。

在混合模拟中,使用的 SPICE 集约模型是BSIM3V3。晶体管的尺寸与器件模型一样。其他重要的尺寸(如源区/漏区面积,P 阱接触面积,P 阱接触与主动器件的距离等)是由 SMIC 提供的版图规则设定。

下面的讨论中,我们将使用文献[9]中定义的概念。直接被粒子轰击的器件称为主器件,而发生电荷共享的器件称为从器件。模拟中,我们固定两个器件间的 STI 宽度为 140nm,改变 STI 深度,即改变了 STI 纵横比。表 1 给出了模拟中使用的 STI 深度和纵横比。

表 1 模拟中使用的 STI 深度和纵横比

Tab.1 Depth and depth-width-ratio of STI in simulation

| STI 深度(μm) | STI 纵横比 |

|------------|---------|

| 0.36       | 2.57    |

| 0.40       | 2.86    |

| 0.45       | 3.21    |

| 0.50       | 3.57    |

| 0.55       | 3.93    |

| 0.60       | 4.29    |

所有的模拟都是在 16 核心 128G 内存的高性能服务器上运行的。整个器件模拟的体积为  $10\mu m \times 10\mu m \times 5\mu m$ ,且器件模型包含 100~000 – 150~000 个网格点。8 个线程的器件模拟的平均时间大约为 1 天。

## 2 模拟结果及分析

#### 2.1 电流形状分析

## 2.1.1 NMOS

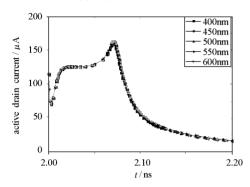

图 3 显示了不同 STI 深度下主 NMOS 的漏端电流。随着 STI 深度的增加,漏端电流基本不发生变化。图 4 给出了从 NMOS 在不同 STI 深度下的漏源端电流。随着 STI 深度从 400nm 增加到550nm 时,从 NMOS 漏端电流峰值增大,而源端变化较小,当 STI 深度超过550nm 时,源漏电流都不再发生变化。这说明550nm 是抑制 NMOS 电荷共享的有效深度,超过这个深度,丛器件漏端电荷收集变化不大。这是因为 NMOS 电荷共享的主要机

理是电荷扩散,而增大 STI 深度相当于使电荷扩散的时间延长,当 STI 的深度增加到使电荷扩散到从器件漏端的时间大于阱接触的时间,多数电荷将被阱接触收集,少量的电荷扩散到从器件漏端。这个使电荷扩散到从器件漏端的时间等于到阱接触时间的 STI 深度称为有效抑制深度。由于校准的器件可以在一定程度上代表真实器件,因而 NMOS 有效抑制深度为 550nm。

图 3 不同 STI 深度下主 NMOS 漏端电流(active drain,即主器件漏端; passive drain,即从器件漏端,passive source,即从器件源端,下同)

Fig. 3 Drain currents of active NMOS for different STI depth(active drain, the drain of active devices; passive drain, the source of passive devices)

图 4 不同 STI 深度下从 NMOS 源漏端电流 Fig. 4 Source and drain currents of passive NMOS for different STI depth

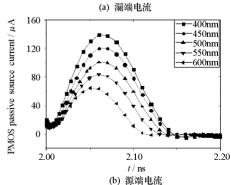

#### 2.1.2 PMOS

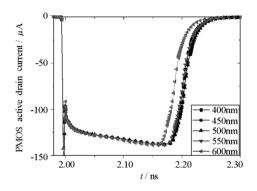

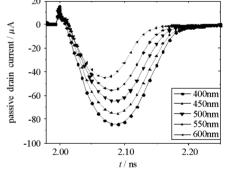

图 5 显示了不同 STI 深度下主 PMOS 的漏端电流。随着 STI 深度的增加,电流持续时间基本

保持不变,当 STI 深度超过 550nm 时,电流持续时间减小。这是因为 PMOS 电荷共享的主要机理是双极放大效应,当 STI 深度增加到 550nm 后,空穴向从器件扩散被抑制,主器件源端附近空穴数目增多,电势变化减弱,注入 N 阱的空穴减少,漏端收集电荷减少。图 6 给出了从 PMOS 在不同 STI 深度下的源漏端电流。随着 STI 深度的增加,从 PMOS 源端和漏端电流的峰值和持续时间都减小。这是因为更深的 STI 深度对电荷扩散抑制越强,导致从 PMOS 源端附近阱电势扰动减小,双极放大效应减弱,从 PMOS 源端注入阱的空穴减小,漏端收集电荷减少。这种抑制作用是线性的,即 STI 深度和从 PMOS 双极放大效应呈线性关系。

图 5 不同 STI 深度下主 PMOS 漏端电流 Fig. 5 Drain currents of active PMOS for different STI depth

图 6 不同 STI 深度下从 PMOS 源漏端电流 Fig. 6 Source and drain currents of passive PMOS for different STI depth

### 2.2 电荷收集分析

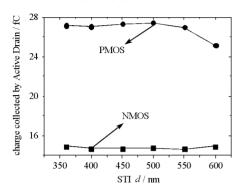

随着 STI 深度的增加,主 NMOS 漏端收集电荷增加。而对于主 PMOS,当 STI 深度从 360nm 增加到 550nm 时,漏端收集的电荷基本保持不变;超过 550nm 后收集电荷降低,如图 7 所示。

图 7 主 NMOS 和主 PMOS 漏端收集电荷 随 STI 深度的变化

Fig. 7 Charge sharing collection at the active NMOS and PMOS versus STI depth

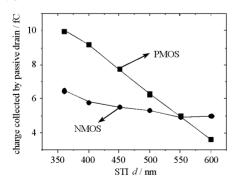

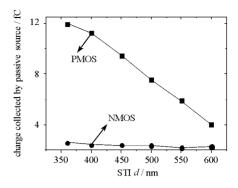

图 8 和图 9 分别给出了从 NMOS 和从 PMOS 漏端收集电荷以及源端注入电荷随 STI 深度的变化。对从 NMOS 来说,漏端收集的电荷随着 STI 深度的增加从 6.48fC 减少到 4.92fC,约降低 24%,而源端基本没有变化。这是因为 NMOS 电荷共享的主要机理是扩散,STI 深度的增加抑制了电荷的扩散。对于从 PMOS 来说,漏端收集电荷和源端注入电荷随 STI 深度的增加线性减小。对曲线拟合得到从 PMOS 漏端电荷收集随 STI 深度变化的公式为:

$$Q_{\text{passive drain}} = -35.8d + 11.2$$

其中, $Q_{\text{passive\_drain}}$ 为从 PMOS 漏端收集的电荷,d 为 STI 深度。

图 8 从 NMOS 和从 PMOS 漏端收集电荷 随 STI 深度的变化

Fig. 8 Charge sharing collection at the passive NMOS and PMOS versus STI depth

## 3 结论

本文研究了不同 STI 深度下,从 NMOS 之间

图 9 从 NMOS 和从 PMOS 源端注入电荷 随 STI 深度的变化

Fig. 9 Injection charge of passive NMOS and PMOS versus STI depth

和从 PMOS 之间电荷共享的变化趋势,发现 STI 深度的增加能有效抑制电荷的扩散,进而抑制电荷共享。550nm 是抑制 NMOS 电荷共享有效 STI 深度,超过这个深度对抑制电荷共享贡献不大;而对于 PMOS, STI 深度的增加使电荷共享线性减弱。此外,拟合的从 PMOS 漏端电荷收集随 STI 深度变化的公式,可以用于 STI 深度的选择。

## 参考文献:

- [1] Amusan O A, Witulski A F, Massengill L W, et al. Charge Collection and Charge Sharing in a 130 nm CMOS Technology [J]. IEEE Trans. Nucl. Sci., Dec. 2006, 53(6): 3253 – 3258.

- [2] Zoutendyk J A, Edmonds L D, Smith L S. Characterization of Multiplebit Errors from Single-ion Tracks in Integrated Circuits [J]. IEEE Trans. Nucl. Sci., Dec. 1989, 36(6); 2267 – 2274.

- [3] Olson B D, Ball D R, Warren K M, et al. Simultaneous Single Event Charge Sharing and Parasitic Bipolar Conduction in a Highlyscaled SRAM Design [J]. IEEE Trans. Nucl. Sci., Dec. 2005, 52(6): 2132 – 2136.

- [4] Amusan O A, Stemberg A L, Witulski A F, et al. Single Event Upsets in a 130 nm Hardened Latch Design Due to Charge Sharing[C]//Proc. 45th Int. Reliability Physics Symp., Arizona, USA, 2007: 306-311.

- [5] Lawrence R K, Kelly A T. Single Event Effect Induced Multiple Cell Upsets in a Commercial 90 nm CMOS Digital Technology [J]. IEEE Trans. Nucl. Sci., Dec. 2008, 55(6): 3367 – 3374.

- [6] Amusan O A. Effect of Single-event-induced Charge Sharing in Sub - 100 nm Bulk CMOS Technology [D]. Vanderbilt University, 2006.

- [7] Amusan O A, Massengill L W, Baze M P, et al. Mitigation Techniques for Single Event Induced Charge Sharing in a 90 nm Bulk CMOS Process [C]//Proc. 46th Int. Reliability Physics Symp., Phoenix, USA, 468 – 472.

- [8] Mikoshiba H, Homma T, Hamano K. A New Trench Isolation Technology as a Replacement of LOCOS [C]//IEEE IEDM Tech. Dig. 1984;578-581.

- [9] Amusan O A, Witulski A F, Massengill L W, et al. Charge Collection and Charge Sharing in a 130 nm CMOS Technology [J]. IEEE Trans. Nucl. Sci., Dec. 2006, 53(6): 3253 – 3258.