doi:10.11887/j.cn.202102008

http://journal. nudt. edu. cn

## 低调谐增益变化的 10 GHz 电感电容式压控振荡器设计\*

齐晓斐,于 杰,孙旭涛,高铭阳,张志勇,赵 武 (西北大学信息科学与技术学院,陕西西安 710127)

摘 要:基于 0.18 μm CMOS 工艺,设计了一种应用于无线通信和雷达系统的低变化调谐增益的电感电容式压控振荡器。该电路包括分布式偏置可变电容阵列和开关电容阵列,合理选择偏置电压扩展电容 - 电压曲线覆盖范围,在整个调谐电压范围内,可有效降低调谐增益。三位开关电容阵列将整个可调频率范围分为8个子频带,通过控制可变电容实现子频带内频率的调谐范围。同时采用开关可变电容阵列,有效抑制了电感电容式压控振荡器调谐增益的变化。基于 1P6M 0.18 μm 工艺模型的后仿真结果显示该 10 GHz 压控振荡器调谐增益变化率表现优异,低至 21.5%,调谐频率范围为 9.13 ~ 11.15 GHz,同时该压控振荡器能够实现较低的直流功耗 9 mW(1.8 V 电源电压),相位噪声在 10 GHz 时为 - 105 dBc/Hz@ 1 MHz。

**关键词:**压控振荡器;调谐增益;分布式偏置可变电容阵列;开关电容阵列;开关可变电容阵列 中图分类号:TN432 文献标志码:A 文章编号:1001 - 2486(2021)02 - 054 - 07

# Design of a 10 GHz LC-VCO with low tuning gain fluctuation

QI Xiaofei, YU Jie, SUN Xutao, GAO Mingyang, ZHANG Zhiyong, ZHAO Wu (School of Information Science and Technology, Northwest University, Xi'an 710127, China)

Abstract: Based on 0.18 μm CMOS process, a low-variable tuning gain LC-VCO(inductance capacitance-voltage controlled oscillator) was designed for wireless communication and radar systems. The circuit includes a distributed bias varactor array and a switched capacitor array, a reasonable selection of the bias voltage can achieve the purpose of expanding the C-V(capacitance-voltage) curve, thereby effectively reducing the tuning gain within the entire tuning voltage range. The three-bit switched capacitor array divides the entire adjustable frequency range into 8 subbands, which is implemented by controlling the varactor array. And the switched varactor array is adopted, which can effectively suppress the variation of the LC-VCO tuning gain. Based on the model of 1P6M 0.18 μm technology, the post-layout simulation results show the good performance on property of tuning gain variation rate, which is 21.5% with the frequency tuning range from 9.13 GHz to 11.15 GHz, at the same time, the VCO DC power consumption is 9 mW with 1.8 V supply voltage, the phase noise is -105 dBc/Hz@1 MHz when the VCO oscillating frequency is around 10 GHz.

Keywords: VCO; tuning gain; distributed biased varactor array; switched capacitor array; switched varactor array

射频芯片是无线通信与雷达系统的核心,压控振荡器(Voltage Controlled Oscillator, VCO)是射频电路的关键模块<sup>[1]</sup>,作为锁相环(Phase Locked Loop, PLL)的核心电路,为整个无线收发系统提供本振信号,其各项性能指标直接影响锁相环及其关联模块的工作性能<sup>[2]</sup>。

调谐增益(K<sub>vco</sub>)决定了 VCO 的频率调谐范围,同时影响 PLL 环路噪声和环路稳定性。为了满足压控振荡器足够宽的频率覆盖范围,传统的降低调谐增益的方法是采用开关电容阵列,选择合适的开关位数来保持较低的调谐增益,以方便设计环路滤波器。但是当频率范围较宽时,即使

开关电容阵列位数较高,调谐增益仍会发生明显的波动,对 PLL 控制环路稳定性的计算造成一定误差<sup>[3]</sup>。因此,获得更低的调谐增益来确保较低的相位噪声并满足锁相环环路滤波器设计的需求是 VCO 设计关注的重点。例如,文献[4]采用开关电容阵列获得多个子频带,满足频率覆盖范围的同时,降低压控振荡器调谐增益,减小相位噪声;文献[5]综合使用可变电容阵列和固定电容阵列,获得较小的压控增益变化;文献[6]选用合适位数的开关电容阵列,同时满足低调谐增益和宽调谐范围的要求;文献[7]使用开关电容阵列,加大可变电容和滤波电容获得优化后的频率调谐

<sup>\*</sup> 收稿日期:2020-01-07

**基金项目:**国家自然科学基金资助项目(61904148);陕西省重点研发计划资助项目(2018GY - 025);西安市科技创新计划资助项目(201805041YD19CG25(1))

作者简介: 齐晓斐(1979—), 女, 陕西西安人, 博士研究生, E-mail; qixf@ nwu. edu. cn; 张志勇(通信作者), 男, 教授, 博士, 博士生导师, E-mail; zhangzy@ nwu. edu. cn

范围与相位噪声。

针对低调谐增益变化的研究包括文献[8-9],相较本设计,应用的射频频段较低;其他低功 耗、低相位噪声、高效率 VCO 的研究如文 献[10-11],其调谐增益变化明显过大。因此, 为了更好地降低 VCO 的调谐增益以及调谐增益 的变化量( $\Delta K_{\text{VCO}}$ ),本文基于 0.18  $\mu$ m 工艺设计 了一种应用于无线通信系统或雷达系统的低调谐 增益变化的 10 GHz 电感电容式压控振荡器 Oscillator, LC-VCO)。该压控振荡器采用电流偏 置型负阻结构,负阻元件由交叉耦合金属氧化物 半导体 (Metal Oxide Semiconductor, MOS) 管实 现,带隙基准源电路产生的电流经过 MOS 管构成 的电流镜结构为压控振荡器提供偏置电流,使其 工作在电流受限区。电阻和 MOS 管选择相应数 值构成低通滤波器,滤除源自基准源的高频噪声。 VCO 的谐振腔由分布式偏置可变电容阵列、开关 电容阵列、开关可变电容阵列构成的总等效电容 和电感组成。该压控振荡器的核心电路包括分布 式偏置可变电容阵列和开关电容阵列,扩展电 容 - 电压(Capacitance-Voltage, C-V) 曲线覆盖范 围,从而在整个调谐电压范围内有效降低调谐增 益。三位开关电容阵列将整个可调频率范围分为 8 个子频带, 子频带内频率的调谐范围通过控制 可变电容实现,同时引入开关可变电容阵列,总的 可变电容值逐位可调,以补偿不同子频带间总电 容变化的不一致性,从而达到有效抑制 LC-VCO 调谐增益变化率的目的。

## 1 电路分析与设计

#### 1.1 调谐增益的变化及其影响

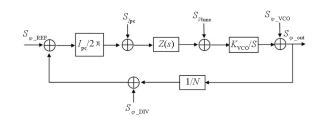

压控振荡器调谐增益的变化对锁相环的性能及环路滤波器的设计有重要影响。较低的调谐增益能够降低环路滤波器的设计难度,减少锁相环对环路噪声的响应程度。而 VCO 及其锁相环系统在整个频率范围内的相位噪声和稳定性很大程度上取决于调谐增益的变化量 $^{[12-13]}$ 。以电荷泵锁相环为例,PLL 各理想模块中,参考信号(REFerence,REF)、VCO 和分频器(DIVider,DIV)的相位噪声功率谱密度等效为 $S_{\varphi\_REF}$ 、 $S_{\varphi\_VCO}$ 和 $S_{\varphi\_DIV}$ ,鉴频鉴相器(Phase Frequency Detector,PFD)和电荷泵(Charge Pump,CP)的电流噪声功率谱密度等效为 $S_{Ipc}$ ,环路滤波器的电压噪声功率谱密度为 $S_{Vtune}$ ,如图 1 所示。

可得到环路开环时锁相环输入和输出端的相

图 1 电荷泵锁相环线性相位噪声模型 Fig. 1 Linear phase noise model of charge pump phase-locked loop

位噪声功率谱密度为

$$S_{\varphi_{-\text{IN}}}(f) = S_{\varphi_{-\text{REF}}}(f) + S_{\varphi_{-\text{DIV}}}(f) + S_{\text{Ipc}}(f) \cdot \left(\frac{2\pi}{I\text{pc}}\right)^{2}$$

(1)

$$S_{\varphi_{-}\text{OUT}}(f) = S_{\varphi_{-}\text{VCO}}(f) + S_{\text{Vtune}}(f) \cdot \left(\frac{K_{\text{VCO}}}{2\pi f}\right)^{2} (2)$$

由式(2)可知,调谐增益直接影响 PLL 环路相位噪声功率谱密度,进而影响环路噪声传递函数,因此锁相环设计时,为了实现较低的相位噪声,需要压控振荡器具有变化率小的低调谐增益。

LC-VCO 的输出频率[14]可表示为

$$f = \frac{1}{2\pi \sqrt{LC}} \tag{3}$$

式中:L 为谐振电感;C 为谐振总电容,其调谐增益  $K_{\text{vco}}$ 可表示 $^{[14]}$ 为

$$K_{\text{VCO}} = \frac{\Delta f}{\Delta C} \times \frac{\Delta C}{\Delta V_{\text{tune}}} = \frac{-1}{4\pi C \sqrt{LC}} \times \frac{\Delta C_{\text{VAR}}}{\Delta V_{\text{tune}}} \quad (4)$$

其中, $C_{VAR}$ 为接入谐振回路的可变电容, $V_{tune}$ 为调谐电压。由式(4)可知,主要由两个因素导致调谐增益变化:某一子频带不同调谐区域上调谐增益的变化来自其可变电容工艺模型的非线性因素;不同子频带间调谐增益的变化来自开关电容位数变化带来谐振总电容 C 变化的不一致性因素。因此可以从这两点入手对电路结构进行优化设计。

#### 1.2 具体电路设计

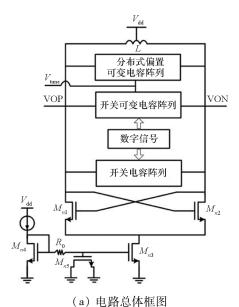

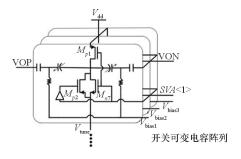

本文设计的电感电容式压控振荡器采用电流偏置型负阻结构,如图 2 所示。负阻元件由交叉耦合 MOS 管  $M_{n1}$ 和  $M_{n2}$ 实现,带隙基准源电路产生的电流经过  $M_{n3}$ 和  $M_{n4}$ 管构成的电流镜结构为压控振荡器提供偏置电流,使其工作在电流受限区。 $R_0$  和  $M_{n5}$ 选择相应数值构成低通滤波器滤除源自基准源的高频噪声。VCO 的谐振腔由分布式偏置可变电容阵列、开关电容阵列、开关可变电容阵列及电感组成。

1.2.1 分布式偏置可变电容阵列设计

如图 3 所示,可变电容由单个参考电压偏置,

(a) Circuit block diagram

- (b) 分布式偏置可变电容阵列

- (b) Distributed bias varactor array

(c) 开关电容阵列

(c) Switched capacitor array

- (d) 开关可变电容阵列

- (d) Switched varactor array

图 2 LC-VCO 电路结构

Fig. 2 Structure of the LC-VCO

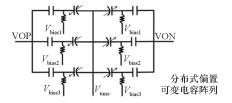

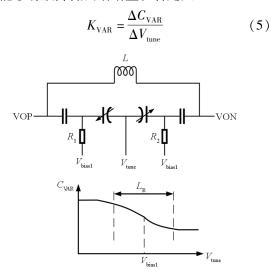

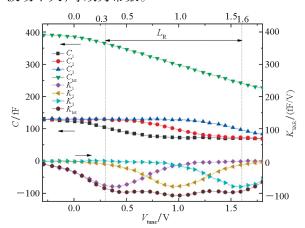

其 C-V 曲线线性区较窄,其余部分相对平坦<sup>[15]</sup>。 采用图 2(b) 所示的分布式偏置可变电容阵列结构,基于图 3 中 C-V 曲线线性区的偏置电压范围,分别调节  $V_{\text{bias2}}$ 、 $V_{\text{bias2}}$ ,可以使线性区不同分布的三条曲线  $C_1$ 、 $C_2$  和  $C_3$  (中间段) 叠加形成图中上方的  $C_{\text{tot}}$  曲线,达到拓展 C-V 曲线线性区

的目的,如图 4 所示。从而在整个调谐电压范围内,能够有效降低调谐增益。若定义

图 3 单参考电压偏置电容 C-V 曲线

Fig. 3 Single reference voltage bias capacitor C-V curve 表示可变电容对调谐电压的敏感度, $C_1$ 、 $C_2$ 、 $C_3$  和  $C_{tot}$  曲线对调谐电压求导曲线分别为图中下方的  $K_1$ 、 $K_2$ 、 $K_3$  和  $K_{tot}$ ,从图 4 可以看出,调谐范围拓展至  $0.3 \sim 1.6$  V,在该电压范围内变化时, $K_{tot}$ 基本波动不大,等效为常数。

图 4 可变电容结构 C-V 特性仿真曲线

Fig. 4 Simulation characteristic of the varactor

#### 1.2.2 开关电容阵列设计

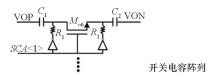

本文采用的开关电容阵列示意图见图 2(c),由 N 型开关管  $M_{n6}$ 和固定电容  $C_1$ 、 $C_2$  串联组成。电阻  $R_1$  用于提供直流参考电位。在开关全部导通时, VCO 工作在低频段; 在开关全部断开时工作于高频段。三位开关电容阵列  $SCA < 2:0 > (000 \sim 111$  作为选频码) 将整个可调频率范围分为8个子频带(000 为频率最高的子频带,111为频率最低的子频带),子频带内频率的调谐范围是通过控制可变电容来实现。开关管  $M_{n6}$  导通时可简单等效一个阻值为  $R_{con}$  的电阻 [16],其

值为

$$\begin{cases}

R_{\text{on}} = \frac{1}{g_{\text{ds}}} \\

g_{\text{ds}} = \mu_n C_{ox} \frac{W}{L} (V_{\text{GS}} - V_{\text{TH}})

\end{cases}$$

(6)

式中: $\mu_n$ 、 $C_{ox}$ 、W和 L分别是迁移率、单位面积栅氧化层电容、栅宽和栅长; $V_{GS}$ 和  $V_{TH}$ 分别为栅源电压和阈值电压。当开关管处于关断状态时可等效为一个电容,等效电容值与开关管的尺寸有关。开关管尺寸太小则会增大导通电阻,降低谐振回路的品质因数,尺寸太大会增加寄生电容,降低调谐效果。

随着开关电容的引入,相邻的子频带必须保证足够的交叠,以确保整个频率范围连续可调。 1.2.3 开关可变电容阵列设计

由式(4)可推导出,调谐增益变化量  $\Delta K_{\text{vco}}$ 与振荡频率变化量  $\Delta f$  之间的表达式为

$$\Delta K_{\text{\tiny VCO}} = \left( A \, \frac{\Delta B}{\Delta f} + B \, \frac{\Delta A}{\Delta f} \right) \Delta f \tag{7}$$

其中

$$A = \frac{-1}{4\pi C \sqrt{LC}} \tag{8}$$

$$B = K_{\text{VAR}} = \frac{\Delta C_{\text{VAR}}}{\Delta V_{\text{turns}}} \tag{9}$$

采用分布式偏置可变电容阵列时,对于给定的电感值,调谐增益  $K_{\text{VCO}} \simeq \frac{-1}{4\pi C \sqrt{LC}}$ ,由图 4 可知,在

线性调谐范围内 B 为定值,则 $\frac{\Delta B}{\Delta f}$  = 0,因此由式(7)得到:

$$\Delta K_{\rm VCO} = B\Delta A \tag{10}$$

由式(10)可知,影响调谐增益变化的主要原因是  $\Delta A$  中 C 的变化,不同调谐曲线随着开关电容的引入,谐振总电容 C 发生变化,引起调谐增益的变化。

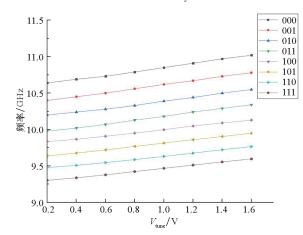

加入开关可变电容阵列后,式(7)中B不再是一个定值,A中的电容随振荡频率增大  $\Delta C$  时, A 减小,而 B 中的  $\Delta C_{\text{VAR}}/\Delta V_{\text{tune}}$ 会随振荡频率增大,即通过 B 随着振荡频率的变化抵消 A 的变化,有效抑制增益变化率。图 5、图 6 分别是未加入开关可变电容阵列和加入开关可变电容阵列的前仿真结果。调谐增益变化率测量值可定义为

$$dK_{VCO} = \frac{K_{VCO,max} - K_{VCO,min}}{K_{VCO,max}}$$

(11)

通过式(11)计算,加入开关可变电容阵列后,调谐增益的变化率降低了12%。

图 5 未加入开关可变电容阵列的频率调谐曲线 Fig. 5 Frequency tuning curve without switched varactor array

图 6 加入开关可变电容阵列的频率调谐曲线 Fig. 6 Frequency tuning curves with switched varactor arrays

本文采用的新型开关可变电容阵列<sup>[17]</sup>由固定电容、积累型可变电容、MOS 开关管和电阻组成,如图 2(d) 所示。 $M_{p2}$ 和  $M_{n7}$ 构成传输门,由SVA < 2:0 > 提供开关可变电容阵列的控制信号。

当控制信号  $SVA < 1 > 为低电平时, M_{p1}$  导通,传输门  $M_{p2}$ 和  $M_{n7}$ 截止,调谐电压被隔断,可变电容固定在最小值,此时的电容 Q 值为

$$Q = R_P C_{\omega} \tag{12}$$

此时

$$R_{P} = R_{\text{onl}} = \frac{1}{\mu_{p} C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

(13)

其中: $R_{\text{onl}}$ 为控制开关  $M_{\text{pl}}$ 的导通电阻; 当 SVA < 1 > 为高电平时, $M_{\text{pl}}$  截止,传输门  $M_{\text{pl}}$  和  $M_{\text{nl}}$  导通,调谐电压  $V_{\text{tune}}$  能够传递以控制可变电容,此时两个开关可变电容接入电路。

$$R_P = \frac{2}{C_{\text{sVAR}}^2 \omega^2 R_{\text{on2}}} \tag{14}$$

开关可变电容的 Q 值为

$$Q_{\text{sVAR}} = \frac{2}{C_{\text{sVAR}} \omega R_{\text{on}2}}$$

(15)

其中

$$R_{\text{on2}} = \frac{\mu_n \mu_p C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}{\mu_n + \mu_p}$$

(16)

$R_{on2}$ 为传输门  $M_{\rho2}$ 和  $M_{n7}$ 并联的导通电阻。故由式(15)可知,开关可变电容的 Q 值与传输门  $M_{\rho2}$ 和  $M_{n7}$ 的导通电阻  $R_{on2}$ 成反比,而  $R_{on2}$ 与传输门  $M_{\rho2}$ 和  $M_{n7}$ 的宽长比成正比,即开关可变电容的 Q 值与传输门  $M_{\rho2}$ 和  $M_{n7}$ 的宽长比成反比,但当传输门截止时, $M_{\rho2}$ 和  $M_{n7}$ 的漏极寄生电容会随宽长比变大而变大,进而影响整个谐振回路的 Q 值, $M_{p1}$ 同理。

因此,适当选取  $M_{p1}$ 、 $M_{p2}$ 、 $M_{n7}$ 尺寸以保持此部分开关可变电容较高的 Q 值而不影响谐振腔的 Q 值。

### 2 版图设计和后仿真结果

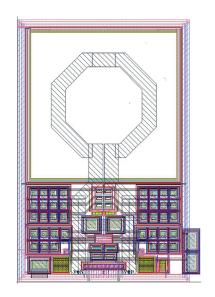

本文设计的 VCO 采用 0.18 μm COMS 工艺, 核心电路版图如图 7 所示。版图采用完全对称的 形式,保证 VCO 优异的匹配性。为了减小寄生效 应,电感两端的引线采用与衬底寄生电容最小的 顶层金属,减小走线长度以提高整个谐振回路的 *Q* 值。

图 7 LC-VCO 核心电路版图 Fig. 7 Layout of the LC-VCO core

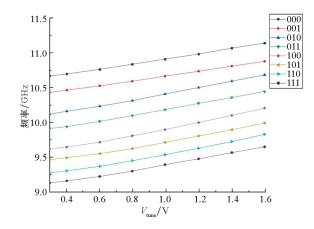

后仿真结果如下:工作电压 1.8 V,控制电压为 0.3~1.6 V,当加入开关可变电容时,调谐曲线相邻子带之间交叠达 50%,输出频率变化为 9.13~11.15 GHz,其 VCO 调谐曲线如图 8

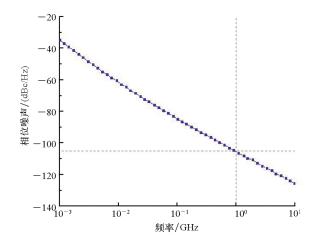

所示。由式(11)得出该压控振荡器加入开关可变电容阵列后,调谐增益变化率为21.5%,1 MHz时相位噪声为-105 dBc/Hz,如图9所示。

图 8 频率调谐曲线 Fig. 8 Frequency tuning curve

图 9 相位噪声特性曲线 Fig. 9 Phase noise characteristic curve

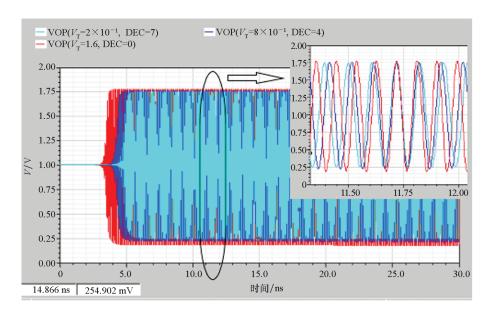

VCO 后仿真的瞬态输出波形见图 10,其中

DEC 为调谐曲线的选频码,用来设置 SCA < 2:0 > 和 SVA < 2:0 > , $V_T$  为调谐电压。从图 10 中可知,DEC = 111 , $V_T = 0.2$  V 为最低输出频率; DEC = 4 , $V_T = 0.8$  V 为中心频率; DEC = 0 , $V_T = 1.6$  V 为最高频率。

后仿真结果频带间变化量的不一致性在于寄生参数的非线性影响,需要根据流片后模块的实测结果,针对性地优化版图以降低影响,或者对开关及相应的阵列进行微调来抵消实测得到的非线性影响。

VCO设计的性能参数有中心频率、调谐范围、相位噪声及功耗等,品质因数(Figure Of Merit, FOM)是衡量此设计整体性能的综合指标,其定义为:

图 10 瞬态输出波形

Fig. 10 Transient output waveform

$$F_{\text{OM}} = L_{\Delta f} - 20 \lg \left(\frac{f_0}{\Delta f}\right) + 10 \lg \frac{P_{\text{DC}}}{P} \tag{17}$$

式中 $,f_0$  为谐振频率 $,L_{\Delta f}$ 为在频偏 $\Delta f$  处的相位噪声 $,P_{\rm DC}$ 是直流功耗,参考功率P的值为 $1~{\rm mW}$ 。

表1列出了本文设计的 LC-VCO 与相同工艺下(CMOS 0.18 μm)其他文献所设计 LC-VCO 的性能比较。可以看出本文设计的 VCO 在调谐增

益变化方面表现最为突出,振荡频率和调谐范围相比其他参考文献也具有一定的优势。VCO的折中设计基于合理的  $F_{OM}$  值来权衡各项性能的指标要求。本设计  $F_{OM}$  为 176 dBc/Hz,相近或优于其他文献 [18-22] 的该项指标,实现了频率调谐范围、功耗、相噪和调谐增益变化率之间的折中设计。

表 1 几种 0.18 μm 工艺下 LC-VCO 的性能参数比较

Tab. 1 Performance comparison of LC-VCOs on 0.18 μm

| 性能参数                      | 工 艺   |           |        |        |             |        |           |            |        |        |

|---------------------------|-------|-----------|--------|--------|-------------|--------|-----------|------------|--------|--------|

|                           | 本文    | 文献[8]     | 文献[9]  | 文献[10] | 文献[11]      | 文献[18] | 文献[19]    | 文献[20]     | 文献[21] | 文献[22] |

| 电源电压/V                    | 1.8   | 1.5       | 1.8    | 1.8    | 1.8         | 1.8    | 1.8       | 1.8        | 1.4    | 2.5    |

| 功耗/mW                     | 9     | 9         | 8      | 9      | 3.06 ~ 3.78 | 8      | 25        | 18         | 9.8    | 15.84  |

| 频率/GHz                    | 10.23 | 1.17 ~2.0 | 5.5    | 3.018  | 3.2 & 2.4   | 5.35   | 24        | 2.05 ~ 2.7 | 10.6   | 3.6    |

| 调谐范围/%                    | 19.92 | 53.8      | 15.7   | 44     | 18.8 & 13   | 18     | 12.6      | 29         |        |        |

| 相噪/(dBc/Hz@1 MHz)         | - 105 | -126      | -112   | - 124  | -118 ~ -112 | -128.4 | -101.3    | -119.5     | - 108  | - 129  |

| 调谐增益变化/%                  | 21.5  | 25.8      | 22     | 123.1  | 35 & 36.8   |        |           |            |        |        |

| $F_{ m om}/({ m dBc/Hz})$ | - 176 |           | -177.2 | -184.4 |             | - 194  | - 176. 93 | -183.8     |        |        |

### 3 结论

本文在 0.18 µm 工艺下设计实现了低变化调谐增益 LC-VCO。设计采用分布式偏置可变电容阵列和开关电容阵列,有效降低调谐增益,并引入新型开关可变电容阵列,能够在保持功耗相对较低的情况下有效抑制调谐增益的变化率。仿真结果表明,输出频率覆盖范围为9.13~11.15 GHz,在整个工作频带内相对最大调谐增

益变化率为 21.5%, 在压控振荡器中心频率为 10 GHz 时, 相位噪声为 - 105 dBc/Hz@1 MHz。在 1.8 V 工作电压下, 功耗为 9 mW。

# 参考文献(References)

- [1] CAO S G, HAN K F, TAN X, et al. A 1.0 V differential VCO in 0.13 µm CMOS technology [J]. Chinese Journal of Semiconductors, 2011, 32(2): 126-129. (in Chinese)

- [2] 戴惜时. 一种高性能宽带 LC-VCO 的设计[J]. 微电子学, 2014, 44(1): 47-50.

- DAI Xishi. Design of a high performance LC-VCO for broadband application [J]. Microelectronics, 2014, 44(1): 47-50. (in Chinese)

- [3] 李仲秋,曾全胜. 锁相环相位噪声与环路带宽的关系分析[J]. 现代电子技术,2009,32(14):132-134.

LI Zhongqiu, ZENG Quansheng. Relationship analysis between PLL phase noise and PLL bandwidth[J]. Modern Electronics Technique, 2009, 32(14):132-134. (in Chinese)

- [4] 唐学锋. 低相位噪声宽带 LC 压控振荡器设计[J]. 电子技术应用, 2015, 41(11): 54-57.

TANG Xuefeng. Design of wide-band LC VCO with low phase noise [J]. Application of Electronic Technique, 2015, 41(11): 54-57. (in Chinese)

- [5] 宋翔. DRM/DAB 接收机中的高性能宽带压控振荡器设计[D]. 南京: 东南大学, 2015.

SONG Xiang. The design of high performance wideband voltage-controlled oscillator in DRM/DAB receiver [D].

Nanjing: Southeast University, 2015. (in Chinese)

- [6] 程福海. 2.4 GHz CMOS 低功耗压控振荡器设计[D]. 南京:东南大学, 2017. CHENG Fuhai. Design of 2.4 GHz CMOS low power VCO[D]. Nanjing: Southeast University, 2017. (in Chinese)

- [7] 王敏,谢生,毛陆虹,等. 一种宽调谐范围的毫米波 LC 压控振荡器设计[J].南京大学学报(自然科学),2020,56(1):151-157. WANG Min, XIE Sheng, MAO Luhong, et al. Design of a mm-wave LC-VCO with a wide tuning range[J]. Journal of Nanjing University (Natural Sciences), 2020,56(1):151-157. (in Chinese)

- [8] 袁路, 唐长文, 闵昊. 一种低调谐增益变化的宽带电感电容压 控 振 荡器 [J]. 半 导 体 学 报, 2008, 29 (5): 1003-1009.

YUAN Lu, TANG Zhangwen, Min Hao. A wideband LC-VCO with small tuning gain fluctuation [J]. Journal of Semiconductors, 2008, 29(5): 1003-1009. (in Chinese)

- [9] 徐雷钧,王超然,白雪.一种新型电容阵列结构线性宽带 VCO[J]. 微电子学,2016,46(6):781-787.

XU Leijun, WANG Chaoran, BAI Xue. A novel capacitor bank for linearized and wide-band VCO [J].

Microelectronics, 2016,46(6):781-787. (in Chinese)

- [10] LUO Y B, MA C Y, GAN Y B, et al. A dual-band CMOS LC-VCO with highly linear frequency tuning characteristics [J]. Microelectronics Journal, 2015, 46(12): 1420-1425.

- [11] 陈顺舟,黄海生,李鑫,等. GPS/BD 接收机中电感电容 压控振荡器设计[J]. 重庆邮电大学学报(自然科学版), 2016,28(3):337-341.

- CHEN Shunzhou, HUANG Haisheng, LI Xin, et al. Design of LC voltage control oscillator for GPS/BD receiver [J]. Journal of Chongqing University of Posts and Telecommunications (Natural Science Edition), 2016, 28(3): 337 341. (in Chinese)

- [12] SUN Y F, YU X Y, RHEE W, et al. Dual-path LC VCO design with partitioned coarse-tuning control in 65 nm CMOS[J]. IEEE Microwave and Wireless Components Letter, 2010, 20(3): 169 171.

- [13] STEPHEN P B, RICHARD R S. A 5-GHz CMOS type-II PLL with low  $K_{\rm VCO}$  and extended fine-tuning range [J]. IEEE Transactions on Microwave Theory and Techniques, 2009, 57(8): 1978 1988.

- [14] BEHZAD R. RF microelectronics [M]. Beijing: Tsinghua University Press, 2003.

- [15] CHEN N, DIAO S X, HUANG L, et al. Design optimizations of phase noise, power consumption and frequency tuning for VCO [J]. Journal of Semiconductors, 2013, 34 (9): 143-148.

- [16] BEHZAD R. Design of analog CMOS integrated circuits M. New York: Mc Graw Hill Education, 2015.

- [17] CAO S G, YANG Y Q, TAN X, et al. A 5 GHz CMOS frequency synthesizer with novel phase-switching prescaler and high-Q LC-VCO [J]. Chinese Journal of Semiconductors, 2011, 32(8): 98 – 103. (in Chinese)

- [18] EMAD E, SASAN N, ALI E, et al. Analytical phase noise study of a back-gate coupled colpits quadrature VCO [J]. Microelectronics Journal, 2020, 100: 104784.

- [19] CHANG Y T, LU H C. A k-band high-efficiency VCO using current reused technique [J]. IEEE Microwave and Wireless Components Letters, 2017, 12(27): 1134 – 1136.

- [20] SÁNCHEZ-AZQUETA C, AGUIRRE J, GIMEO C, et al. High-resolution wide-band LC-VCO for reliable operation in phase-locked loops [J]. Microelectronics Reliability, 2016, 63: 251 – 255.

- [21] HANEN S, MOHANED D, HAMADI G, et al. Design of 10.6 GHz low phase noise LC-voltage controlled oscillator in 0.18 μm CMOS technology [ C ]// Proceedings of International Conference on Sciences and Techniques of Automatic Control and Computer Engineering (STA), 2017: 120 126.

- [22] 张启帆,王建伟,石春琦,等. UHF RFID 读写器中低噪声宽带 VCO 的设计[J]. 固体电子学研究与进展,2015,35(2):150-155.

ZHANG Qifan, WANG Jianwei, SHI Chunqi, et al. A low phase noise and wide-band VCO for UHF RFID reader[J]. Research & Progress of Solid State Electronics, 2015,35(2):150-155. (in Chinese)