doi:10.11887/j.issn.1001-2486.24010004

http://journal. nudt. edu. cn

## 亚 20 nm FinFET SRAM 工艺涨落对单粒子翻转特性的影响

孙 乾 $^{1,2}$ ,郭 阳 $^{1,2*}$ ,梁 斌 $^{1,2}$ ,池雅庆 $^{1,2}$ ,陶 明 $^{3}$ ,罗 登 $^{1,2}$ ,陈建军 $^{1,2}$ , 孙晗晗 $^{1,2}$ ,胡春媚 $^{1,2}$ ,方亚豪 $^{1,2}$ ,高宇林 $^{1,2}$ ,肖 靖 $^{3}$

- (1. 国防科技大学 计算机学院, 湖南 长沙 410073;

- 2. 国防科技大学 先进微处理器芯片与系统重点实验室, 湖南 长沙 410073

- 3. 湖南大学 电气与信息工程学院, 湖南 长沙 410082)

摘 要:为了探究工艺涨落对亚 20 纳米鳍式场效应晶体管(fin field-effect transistor, FinFET)工艺静态随机存储器(static random-access memory, SRAM)单粒子翻转特性的影响,通过建立与商用工艺接近的高精度三维计算机辅助工艺设计模型,对不同工艺角下 FinFET SRAM 的单粒子翻转特性进行仿真。仿真结果显示,FinFET 工艺 SRAM 的单粒子翻转阈值在不同的工艺角变化下产生微小波动,且敏感位置都在 N 型金属氧化物半导体上。为了明确具体的工艺参数涨落对单粒子翻转阈值的影响,对鳍的厚度、鳍的高度、栅氧厚度、功函数波动造成的单粒子翻转特性的影响进行研究。仿真结果表明,前两种因素对翻转阈值未产生影响,后两种因素对翻转阈值造成了微小的波动。首次发现工艺涨落对 FinFET SRAM 单粒子翻转阈值的影响大幅降低,该发现对研制高一致性的抗辐射宇航用集成电路具有重要意义。

关键词:FinFET;单粒子翻转;静态随机存储器;工艺涨落;工艺角

中图分类号:TN405 文献标志码:A 文章编号:1001-2486(2025)06-264-10

文 拓

# Process fluctuation influence on single event upset in sub-20 nm FinFET SRAM

SUN Qian<sup>1,2</sup>, GUO Yang<sup>1,2</sup>\*, LIANG Bin<sup>1,2</sup>, CHI Yaqing<sup>1,2</sup>, TAO Ming<sup>3</sup>, LUO Deng<sup>1,2</sup>, CHEN Jianjun<sup>1,2</sup>, SUN Hanhan<sup>1,2</sup>, HU Chunmei<sup>1,2</sup>, FANG Yahao<sup>1,2</sup>, GAO Yulin<sup>1,2</sup>, XIAO Jing<sup>3</sup>

- (1. College of Computer Science and Technology, National University of Defense Technology, Changsha 410073, China;

- 2. Key Laboratory of Advanced Microprocessor Chips and Systems, National University of Defense Technology, Changsha 410073, China;

- 3. College of Electrical and Information Engineering, Hunan University, Changsha 410082, China)

Abstract: To investigate the process fluctuation influence on SRAM(static random-access memory) single event upset in sub-20 nm FinFET (fin field-effect transistor) process, a high precision three dimensional technology computer-aid design model based on commercial process fluctuations was established, then simulated to find the FinFET SRAM single event upset threshold under different process corners. The simulation results show that the FinFET SRAM upset threshold has less variation induced by process corner fluctuation. Meanwhile, the sensitive positions of SRAM are on the N-complementary metal oxide semiconductor. Then, to understand the the impact of specific process parameter fluctuations on the single event upset threshold, the process fluctuation factor impact on single event upset was discussed, including fin width, fin height, the oxide thickness and the work function fluctuation. The simulation results show that the first two factors did not affect the upset threshold, while the latter two factors caused slight fluctuations in the upset threshold. Significant reduction in the impact of process fluctuations on FinFET SRAM single event upset threshold is firstly found, which is of great significance for the development of highly consistent radiation hardened aerospace integrated circuits.

Keywords: FinFET; single event upset; static random-access memory; process fluctuation; process corner

随着我国太空探索的任务数量和任务复杂度的逐渐提高,火箭和星上载荷需要更高算力的集

成电路。鳍式场效应晶体管(fin field-effect transistor, FinFET)以其更弱的短沟道效应、更小

收稿日期:2024-01-04

基金项目: 国家自然科学基金资助项目(62174180);湖南省研究生科研创新项目资助项目(CX20220005)

第一作者:孙乾(1995—),男,山东枣庄人,博士研究生,E-mail:sungian18@ nudt. edu. cn

\*通信作者:郭阳(1971—),男,浙江东阳人,研究员,博士,博士生导师,E-mail:guoyang@ nudt. edu. cn

引用格式:孙乾,郭阳,梁斌,等. 亚 20 nm FinFET SRAM 工艺涨落对单粒子翻转特性的影响[J]. 国防科技大学学报, 2025, 47(6): 264-273.

Citation: SUN Q, GUO Y, LIANG B, et al. Process fluctuation influence on single event upset in sub-20 nm FinFET SRAM[J]. Journal of National University of Defense Technology, 2025, 47(6): 264-273.

的器件体积和更低的功耗,成为代替平面互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)的下一代逻辑器件。然而在太空中存在着大量的高能粒子和宇宙射线,这些辐射源会严重影响集成电路的稳定工作,造成集成电路功能中断、软错误,甚至永久性器件结构损伤。单粒子翻转(single event upset, SEU)是在集成电路的存储器中产生的瞬态辐照效应,该效应由高能粒子轰击存储数据单元的敏感位置引发,导致存储的数据发生翻转,影响集成电路保存数据的准确性和完整性。六管静态随机存储器(6 transistors-static random-access memory, 6T-SRAM)是集成电路设计中常用的存储器,被广泛用于缓存单元中。SRAM 的抗单粒子翻转特性,直接决定了集成电路在宇宙空间工作的可靠性。

工艺涨落是集成电路在制造的过程中,由于 掩膜形状、离子沉积、金属沉积或刻蚀存在一定误 差,器件的阱和源漏的掺杂浓度、栅氧厚度、栅极 形状发生变化,进而影响晶体管的静态特性和动 态特性。随着晶体管工艺从二维平面器件演进到 三维器件,其工艺涨落的机理更为复杂,对晶体管 性能造成的影响更为显著。工艺涨落对晶体管的 影响主要体现在线边粗糙涨落、金属功函数涨落 和随机掺杂涨落[1],其中的金属功函数涨落和随 机掺杂涨落对晶体管制造的前段工艺造成影响。 与此同时,工艺涨落的相关特性由工艺厂的工程 师整理,建模为工艺角(process corner)模型,便于 电路设计者评估工艺涨落对电路性能、功耗和可 靠性的影响。工艺角信息集成在工艺厂提供的制 程设计套件(process design kit, PDK)中的两个模 型中,分别为后仿提参模型和集成电路仿真程序 ( simulation program with integrated circuits emphasis, SPICE)模型。电路设计工程师使用后 仿提参模型提取相关特征参数,并调用 SPICE 模 型进行仿真,即可表征晶体管性能受到工艺涨落 的影响。

学界已有针对工艺涨落造成器件单粒子效应特性的影响研究。Kauppila等借助蒙特卡罗计算工具,通过修改模型中的SPICE参数,在商用90 nm和65 nm工艺下研究工艺变化对6T-SRAM单粒子翻转特性的影响,研究结果表明,阈值电压、栅氧厚度、结深参数的变化对6T-SRAM翻转的阈值有显著影响,其峰峰值差异最大可达141.9% [2]。Royer等同样使用SPICE工具,对20 nm、14 nm、10 nm 和7 nm FinFET工艺节点下的6T-SRAM开展单粒子翻转阈值的研究,仿真结

果显示,随着节点的缩减,引发 6T-SRAM 翻转的 阈值电荷不断减小,而这之中阈值电压的影响最 为明显<sup>[3]</sup>。Wang 等针对 TSMC 65 nm 工艺,使用 SPICE模型开展了工艺涨落对单粒子瞬态 Quenching 效应影响的研究,研究结果表明,单粒 子瞬态中的 Quenching 效应受到栅氧厚度的影响 最大[4]。以上研究虽然针对晶体管工艺涨落对 单粒子效应的影响进行了部分研究,但是现今对 于 FinFET 器件工艺涨落研究, 乃至 FinFET 标准 单元研究的方法是基于 SPICE 模型和双指数电 流源进行的[5-7],而该方法对于组合逻辑、SRAM 和D触发器单粒子脉冲宽度和翻转阈值的仿真 存在较大误差。另外,虽然其他对 FinFET 器件的 单粒子效应研究是基于三维计算机辅助工艺设计 (technology computer-aid design, TCAD) 工具进行 数值仿真,但其仿真精度受到器件建模精度和电 学特性表征方法的影响[8-14]。学术界使用的 FinFET SRAM 三维 TCAD 模型多基于公开文献 中发表的相关参数进行建模,缺少具体的商用工 艺进行指导,使得建立的模型不符合实际的商用 器件特性,导致研究的成果与实际商用工艺的试 验结果相差甚远。另外,学术界探讨工艺波动对 单粒子效应的影响时,所选择的工艺波动参数往 往是众多发表文献中的最优和最差参数,而在商 用工艺中,这些参数往往是较为稳定的,这往往导 致研究结果与实际制造的电路相比具有较大误 差,不够贴合实际情况。因此,建立一个基于实际 商用工艺的高精度 FinFET SRAM 三维 TCAD 模 型研究工艺涨落对单粒子翻转阈值的影响是亟待 研究的课题。

为研究以上问题,本文使用 TCAD 软件建立 了高精度 FinFET SRAM TCAD 模型,并基于该模 型开展不同工艺涨落条件对 FinFET 工艺下 SRAM 单粒子翻转阈值影响的研究。首先,建立 了一套基于业界常用工艺的高精度 FinFET 6T-SRAM 三维 TCAD 模型,涵盖了 TT(典型工艺)、 FF(最快工艺)、SS(最慢工艺)三种工艺角;之后, 基于建立的 6T-SRAM 三维 TCAD 模型,进行重离 子轰击仿真,并计算其翻转线性能量传输(linear energy transfer, LET) 阈值;最后,基于从 PDK 中 提取出的 FinFET 晶体管关键工艺参数的波动范 围,定量研究相关工艺参数对6T-SRAM翻转阈值 的影响。研究结果表明,相较于传统的平面体硅 工艺,亚20 nm FinFET 工艺涨落对 SRAM 单粒子 翻转阈值的影响大幅降低。该发现对研制高一致 性的抗辐射宇航用集成电路具有重要意义。

## 1 高精度 FinFET SRAM 三维 TCAD 模型 建立与校准

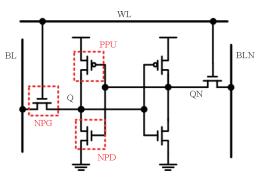

一种典型的 6T-SRAM 单元的电路和晶体管 命名如图 1 所示,其包含 4 个 N 型金属氧化物半 导体(N-metal oxide semiconductor, NMOS)晶体管 和2个P型金属氧化物半导体(P-metal oxide semiconductor, PMOS) 晶体管。按照晶体管的功 能,可将 6T-SRAM 单元中的晶体管分为 N 型下 拉管 (NMOS pull down, NPD)、N 型传输门 (NMOS passing gate, NPG)、P型上拉管(PMOS pull up, PPU)。TCAD 是一种使用有限元计算方 法对半导体器件进行工艺仿真和电学特性仿真 的软件。TCAD 软件可以通过工艺模拟的方法 建立半导体器件模型。工艺模拟即是根据实际 半导体的制造流程,通过沉积、刻蚀、离子注入、 外延生长的方式,使用有限元方法模拟器件的 制造流程,构建相应的半导体器件模型。完成 器件模型建模,即可以进行电学特性仿真。在 电学特性仿真中,仿真器根据用户选择的半导 体物理模型,依据载流子输运方程,基于有限元 计算方法对器件的载流子速度和浓度分布进行 模拟和仿真,得到半导体器件模型的直流特性、 瞬态特性和频率特性。TCAD 软件计算器件的 直流特性和瞬态特性时,使用的静电学方程见 式(1)~(3):

$$\varepsilon \Phi = -q(p - n + N_{\rm D} - N_{\rm A}) - \rho_{\rm trap} \qquad (1)$$

$$\nabla \cdot \boldsymbol{J}_{n} = q(R_{\text{net},n} - G_{\text{net},n}) + q \frac{\partial n}{\partial t}$$

(2)

$$\nabla \cdot \boldsymbol{J}_{p} = q(R_{\text{net},p} - G_{\text{net},p}) + q \frac{\partial p}{\partial t}$$

(3)

式(1)为泊松方程,表示了单位体积内电通量密度的导数,即电场与位置函数的关系,其中 $\nabla$ 为哈密顿算子, $\varepsilon$ 为介电常数, $\Phi$ 为静电势,q为单位电荷,n和p分别表示电子和空穴的密度, $N_{\rm D}$ 和 $N_{\rm A}$ 为掺杂的施主和受主密度, $\rho_{\rm trap}$ 为陷阱电荷密

图 1 6T-SRAM 电路图

Fig. 1 Schematic of 6T-SRAM

度。式(2)和式(3)分别为电子和空穴的连续性方程,该方程表示了单位时间和空间内电子和空穴密度的关系,其中  $J_n$  和  $J_p$  分别为电子和空穴的电流密度, $R_{\text{net},n}$  和  $R_{\text{net},p}$  分别为电子和空穴的电流密度, $R_{\text{net},n}$  和  $R_{\text{net},p}$  分别为电子和空穴的复合率, $G_{\text{net},n}$  和  $G_{\text{net},p}$  分别代表电子和空穴的生成率。针对式(2)和式(3)中的载流子电流密度,需要一系列表示电流密度和电势之间关系的公式,TCAD 软件中选用的物理模型将直接影响载流子电流密度的函数表示。此外,式(2)~(3)中电子和空穴的复合率与生成率由 TCAD 软件中选用的复合模型表示。式(1)~(3)三个非线性偏微分方程组联立,共同构成了 TCAD 仿真的基本数学原理。

为了建立一个高精度的 FinFET SRAM 模型,首先需要使用合适的物理模型进行构建。在 FinFET SRAM TCAD 模型使用的物理模型包括:积累层与反形层迁移率模型、高场饱和模型、薄层迁移率模型、考虑晶相的应力模型、间质 - 硅层间陷阱模型、肖特基 - 里德 - 霍尔(Shockley-Read-Hall, SRH)和俄歇复合模型。

抽取 FinFET 工艺的结构参数是另一个难 题。作为工艺厂的下游用户,获得工艺相关信 息的重要渠道是深入了解工艺厂提供的 PDK。 绝大多数工艺厂会提供 SPICE 模型和电阻 - 电 容抽参模型,用于电路设计的电学特性仿真,其 中便包含了大量的工艺信息。而这之中的 SPICE 模型必须符合伯克利短沟道绝缘栅型场 效应晶体管模型 - 共有多栅型 (Berkeley shortchannel insulated gate field effect transistor model, common multi-gate, BSIM-CMG)模型<sup>[15]</sup>中的参 数定义,其中一部分与 FinFET 的器件结构有直 接关系。因此,根据工艺厂提供的 FinFET SRAM BSIM-CMG 模型参数,结合透射电子显微 镜的拍摄分析结果,总结了该商用工艺下关键 器件参数值,如表1所示,这保证了 FinFET SRAM TCAD 模型的合理性。同时,为了满足在 FF和SS两种工艺角下的研究要求,从SPICE模 型中抽取了与工艺角相关的参数,并将波动值 标注在了表1中。由于商业保密要求,本文无 法在文中提供足够准确的值用于仿真复现,但 是其数量级是正确的。

另外,本模型通过文献[16-27]补充了其余的工艺参数信息,并根据工艺厂提供的标准电流-电压(I-V)特性曲线进行校准。表 2 中展示了这些参数的合理取值范围,并接近于工艺厂实际的制造情况。

#### 表 1 NPG 晶体管在不同工艺角下关键结构和 掺杂的参数值

Tab. 1 NPG transistor geometry and doping parameters in different process corner

| 参数名称       | SS 工艺角<br>下的值      | TT 工艺角<br>下的值      | FF 工艺角<br>下的值      |

|------------|--------------------|--------------------|--------------------|

| <br>功函数/eV | 4.570              | 4. 626             | 4. 680             |

| 沟道掺杂浓度/cm³ | $8 \times 10^{17}$ | $8 \times 10^{17}$ | $8 \times 10^{17}$ |

| 源漏掺杂浓度/cm³ | $2 \times 10^{20}$ | $2 \times 10^{20}$ | $2 \times 10^{20}$ |

| 栅氧厚度/nm    | 1.60               | 1.58               | 1.56               |

| 鳍间距/nm     | 48                 | 48                 | 48                 |

| 鳍高度/nm     | 44.1               | 45.0               | 45.9               |

| 鳍顶厚度/nm    | 4.508              | 4.6                | 4.692              |

| 鳍底厚度/nm    | 13.908             | 14                 | 14. 092            |

表 2 FinFET 器件关键参数取值范围

Tab. 2 Key parameters ranges in FinFET

| 参数名称                                    | 取值范围                                                                |  |  |

|-----------------------------------------|---------------------------------------------------------------------|--|--|

| 线槽隔离应力                                  | 1 GPa 拉应力                                                           |  |  |

| Si <sub>x</sub> Ge <sub>y</sub><br>摩尔分数 | 0.3 < $y$ < 0.7, $ \Re $ $ x$ = 0.5 $ y$ = 0.5                      |  |  |

| Si <sub>x</sub> C <sub>y</sub><br>摩尔分数  | 0. $02 < y < 0.04$ , $$ $\Re 为 x = 0.97$ , $y = 0.03$               |  |  |

| 陷阱浓度                                    | 施主和受主浓度范围在 $1 \times 10^{10} \sim 1 \times 10^{12} \text{ cm}^{-3}$ |  |  |

| 陷阱能带                                    | 能级中带                                                                |  |  |

| 陷阱截面                                    | $1 \times 10^{-19} \sim 1 \times 10^{-10} \text{ cm}^2$             |  |  |

| 高 K 材料                                  | 16 ~ 26                                                             |  |  |

| 介电常数                                    | 16 ~ 26                                                             |  |  |

| 接触电阻                                    | 小于 $5 \times 10^{-8} \Omega/\text{cm}^2$                            |  |  |

| <b></b>                                 | 0.9×10 <sup>7</sup> ~8×10 <sup>7</sup> cm/s,<br>参考 SPICE 中参数        |  |  |

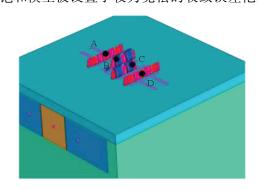

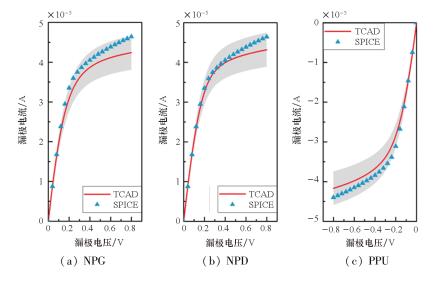

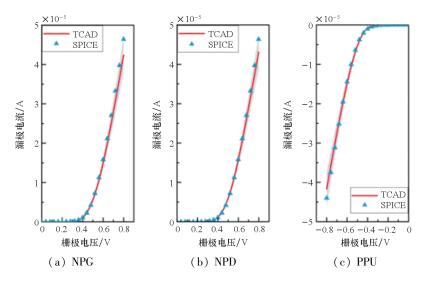

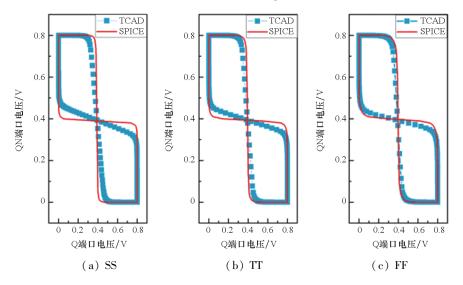

为了证明建模方法的准确性,通过以上数据, 分别构建了在 TT、FF 和 SS 工艺角下,沟道长度 为 16 nm 的 FinFET SRAM TCAD 模型,如图 2 所 示。对三种晶体管进行了三种工艺角下 I-V 特 性的仿真,并与工艺厂提供的 SPICE 模型仿真曲 线进行对比,其TT工艺角下的校准结果如图3和 图 4 所示。图中的紫色区域为以 SPICE 的 I-V特性为基准构建的 ±10% 的误差区间。仿真结果 显示,NPG、NPD、PPU 晶体管的 I-V 曲线在三种 工艺角的条件下误差均在 ±10% 范围内。基于完 成电学特性校准的 6T-SRAM TCAD 模型,通过仿 真蝶形图验证其电学特性,仿真结果见图5。在 所有工艺角下,蝶形图的转换电平与 SPICE 模型 的误差小于 ± 10%, 其中 TT 工艺角下小于 ±1%。值得注意的是,三维 TCAD 模型仿真的跳 变时长却显著长于 SPICE 模型,其原因是 TCAD 模型仿真时使用的高场饱和模型,在晶体管电流 极小(小于10<sup>-8</sup> A)时,由于载流子数量过少,易 使得模型不收敛。为保证模型良好的收敛性,高 场饱和模型被设置了较为宽松的收敛误差范围,

图 2 6T-SRAM 器件三维 TCAD 模型 Fig. 2 6T-SRAM 3D TCAD model

图 3 6T-SRAM 中晶体管  $I_d - V_d$  校准结果

Fig. 3 6T-SRAM transistors  $I_d - V_d$  calibration result

图 4 6T-SRAM 中晶体管  $I_d - V_g$  校准结果

Fig. 4 6T-SRAM transistors  $I_d - V_g$  calibration result

图 5 6T-SRAM 不同工艺角下蝶形图

Fig. 5 Butterfly curve of 6T-SRAM in different process corner

然而这导致在计算关态电流时会比实际情况更大,使得 TCAD 模型中的晶体管相比于 SPICE 模型具有更大的关态电流 (TCAD 模型 10<sup>-10</sup> A, SPICE 模型 10<sup>-11</sup> A),造成更低的亚阈值摆幅。但以上关态电流的误差不会对器件的单粒子特性造成影响。

综上所述,本研究建立的 FinFET SRAM 三维 TCAD 模型具有较好的精度,其在 TT、FF 和 SS 工 艺角下 I-V 和蝶形图特性在关键电学参数上与实际的工艺相比误差均小于  $\pm 10\%$ ,满足进行亚 20 nm FinFET 工艺下 SRAM 单粒子翻转阈值的相关研究要求。

## 2 不同工艺角对单粒子翻转阈值的影响

基于构建的不同工艺角下 FinFET SRAM 三维 TCAD 模型,对其进行重离子辐照仿真,分别探

究当重离子轰击 NMOS 或 PMOS 时,在不同工艺 角下 FinFET SRAM 翻转阈值的变化。根据建立 的多工艺角三维 TCAD SRAM 模型,使用瞬态仿 真的方法进行重离子效应的仿真。重离子效应仿 真中,电子空穴对分布半径为 100 nm<sup>[28]</sup>,且为高 斯分布。利用二分法修改 LET 值,其方法如下: 分别仿真在 LET 为 A 和 B 的条件下 SRAM 的翻 转情况,其中A小于B。如果A和B均发生翻转, 说明翻转阈值小于A,则选取一个小于A 的 LET 值进行仿真,并作为新的 A 值。如果 A 和 B 均未 发生翻转,说明翻转阈值大于B,则选取一个大于 B 的 LET 值进行仿真,并作为新的 B 值。如果 A未出现翻转而B出现了翻转,则翻转阈值在A至 B 中间,之后选择 A 至 B 的中点作为 LET 值进行 仿真,如果新的 LET 值仿真结果为翻转则为 B值,否则为A值。按照以上方法重复仿真,直到A

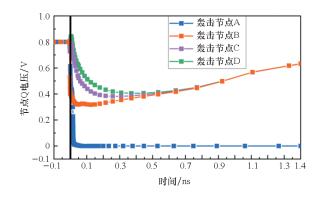

和 B 的差等于 0.1 MeV·cm²/mg,则 B 是该节点下的翻转阈值。仿真中的其他物理模型与 I-V 特性和蝶形图的仿真相同。在对 SRAM 进行轰击前,会先对 SRAM 单元进行赋值,写入的存储数据为 1。对敏感节点——NMOS 和 PMOS 的漏极进行轰击,轰击的位置见图 2,图中的节点 A 和 D 为 NMOS 晶体管的漏极,节点 B 和 C 为 PMOS 晶体管的漏极。节点 A 和 B 相连接,对应图 1 电路中的 Q 节点;节点 C 和 D 相连接,对应图 1 电路中的 QN 节点。由于 SRAM 版图结构的对称性,当 SRAM 单元存储 1 时轰击节点 C 和节点 D,与存储 0 时轰击节点 A 和节点 B 的效果相同,因此决定仿真在存储 1 时轰击节点 A 到 D。

对 FinFET 不同工艺角下 SRAM 三维 TCAD 模型的单粒子翻转阈值仿真结果见表 3,轰击后 节点 Q 的电压变化结果见图 6。图 6 中轰击节点 A 时的 LET 值为 7.0 MeV·cm<sup>2</sup>/mg,其余节点为 120 MeV · cm<sup>2</sup>/mg。若单粒子翻转阈值大于 120 MeV·cm<sup>2</sup>/mg,便可以认为该节点不会受到 重离子影响,为单粒子翻转免疫节点。仿真结果 显示,四个轰击点中只有节点 A 发生了单粒子翻 转,且在三个工艺角下,FF 工艺角具有最高的翻 转阈值,SS和TT工艺角具有最低的翻转阈值,但 三种工艺角的波动变化仅有  $0.1 \text{ MeV} \cdot \text{cm}^2/\text{mg}$ , 工艺波动造成的影响极小。过去针对平面体硅工 艺的研究则认为,SRAM 存储器单粒子翻转阈值 随工艺角会产生显著的波动[2]。以上仿真结果 表明, FinFET 工艺下的 SRAM 的单粒子翻转阈值 基本不受制造过程中工艺涨落的影响,该现象与 平面工艺不同。

#### 表 3 不同工艺角下 SRAM 单粒子翻转阈值仿真结果

Tab. 3 Simulation result of SRAM SEU threshold at various process corner

单位:MeV·cm<sup>2</sup>/mg

| 轰击节点 | SS 工艺角 | TT 工艺角 | FF 工艺角 |

|------|--------|--------|--------|

| A    | 4.0    | 4.0    | 4.1    |

| В    | >120   | >120   | >120   |

| C    | >120   | >120   | >120   |

| D    | >120   | >120   | >120   |

图 6 重离子轰击节点 A~D 时,节点 Q 的电压变化 Fig. 6 Node Q potential variation after heavy-ion hit point A~D

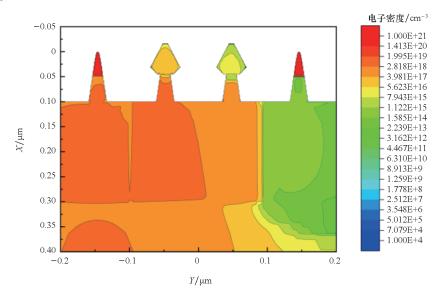

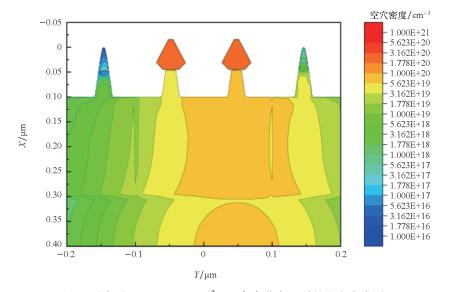

此外,从仿真的结果中可以发现,存储数据为1时与Q节点相连的NMOS晶体管是最敏感的节点,而在过去被认为最容易翻转的与Q节点相连的PMOS晶体管却没有发生翻转。从图7所示重离子轰击的电势变化可究其原因:Quenching效应使得PMOS未发生翻转<sup>[29-31]</sup>。该效应的内容是:当两个晶体管的距离足够近时,重离子轰击其中

(a) 重离子以 7 MeV·cm²/mg 轰击节点 A 时的电子密度图

(a) Electron density snapshot when heavy-ion hit point A with 7 MeV · cm<sup>2</sup>/mg

(b) 重离子以 120 MeV·cm²/mg 轰击节点 C 时的空穴密度图

(b) Hole density snapshot when heavy-ion hit point C with 120 MeV·cm²/mg

图 7 重离子轰击节点 A 和 C 的电子和空穴密度的截面图 Fig. 7 Electron & hole density snapshot after heavy-ion hit node A and C

一个晶体管引发的电子空穴对会影响邻近的晶体管,然而这种情况下,两个相关节点的电势更容易保持为原来的状态,使得两个节点更不容易翻转。在 FinFET 工艺下的 SRAM 单元中,两个晶体管之间的横向间距为 80 nm,纵向间距为 48 nm,纵向的两个晶体管间距小于重离子产生的电子空穴对的半径,引发了 Quenching 效应,使得 PMOS 晶体管反而具有更高的翻转阈值。另外,文献[32]中的试验现象与本研究的仿真现象一致。因此,该仿真结果表明,FinFET 工艺下的 SRAM 敏感节点为存储数据 1 的 NMOS 漏极,这与平面工艺的结论不同。

## 3 不同工艺涨落特性对单粒子翻转阈值的 影响

在初步研究了 FinFET 工艺中 SRAM 存储器在不同工艺角下的单粒子翻转阈值后,需要对各种可能影响单粒子阈值翻转的因素进行定量研究。基于在第1节中得到的实际工艺中各个工艺角参数变化范围,以及学界认为对单粒子效应有影响的因素,本文将研究鳍的厚度、鳍的高度、功函数、栅氧厚度波动对 SRAM 存储器单粒子翻转阈值的影响。目标工艺的鳍的厚度、鳍的高度、栅氧厚度和功函数的参数及波动范围见表4,其波动范围与实际工艺中的波动情况保持一致。研究单一工艺涨落因素对单粒子翻转阈值影响的研究将基于基准参数——TT 工艺角下的参数进行,研究要素的波动范围将根据表4中填写的工艺波动

范围进行。由于在前序研究中,节点 A 为该 FinFET 下 SRAM 的敏感节点,即只有节点 A 存在 翻转阈值,故本节的研究中使用的重离子轰击仿 真将只轰击节点 A,其余的仿真设置同探究工艺 角单粒子翻转阈值研究。

## 表 4 鳍的厚度、鳍的高度、栅氧厚度和 功函数在某商用工艺中的变化范围

Tab.4 The fin thickness, fin height, gate oxide thickness and work function range in a commercial process

| 工艺参数     | 基准<br>参数            | 波动范围                             | 波动<br>幅度/% |

|----------|---------------------|----------------------------------|------------|

| 鳍的平均厚度   | 9.3 nm              | 9.208 ~ 9.392 nm                 | ±1.0       |

| 鳍的高度     | 45.0 nm             | 44.1 ~45.9 nm                    | ±2.0       |

| 栅氧厚度     | 1.58 nm             | 1.56 ~ 1.60 nm                   | ±1.2       |

| NMOS 功函数 | $4.626~\mathrm{eV}$ | $4.570 \sim 4.680 \ \mathrm{eV}$ | ±1.2       |

| PMOS 功函数 | 4.660 eV            | 4.600 ~4.725 eV                  | ±1.2       |

对鳍的厚度和高度的仿真结果见表 5。仿真结果表明,在商用工艺的波动范围中,鳍的厚度和高度不会对单粒子翻转阈值造成影响。究其原因,在实际工艺中鳍的厚度和高度变化十分微小,对 NMOS 和 PMOS 晶体管寄生电容和驱动能力的影响较为均衡,且电荷的沉积量波动不足以使得电荷收集量发生较大改变。而在对栅氧厚度变化对单粒子翻转阈值影响的研究中,观察到了翻转阈值的波动。较厚和较薄的栅氧变化均引起了翻

转阈值的波动,仿真结果见表 5。究其原因,栅氧厚度的变化会使得晶体管的阈值电压和栅极电容发生波动,阈值电压的波动往往会引起 SRAM翻转阈值的变化。然而,由于栅氧的波动变化并不会区分 NMOS 或 PMOS 产生特定的波动,因此栅氧的波动会同时引发 NMOS 和 PMOS 阈值电压的同时变化,使得栅氧引发的翻转阈值未产生趋势性的变化。此外,虽然栅氧厚度会对栅极电容产生影响,但在本商用工艺的波动范围下,其寄生电容的变化相较于重离子轰击产生的电荷收集而言并不显著,因此仿真结果未见其产生影响。

表 5 不同鳍的厚度、鳍的高度和栅氧厚度下的翻转阈值 Tab. 5 The upset threshold under fin thickness, fin height and gate oxide thickness variation

单位:MeV·cm²/mg

| 工艺参数   | SS 工艺角 | TT 工艺角 | FF 工艺角 |

|--------|--------|--------|--------|

| 鳍的平均厚度 | 4.0    | 4.0    | 4.0    |

| 鳍的高度   | 4.0    | 4.0    | 4.0    |

| 栅氧厚度   | 4.1    | 4.0    | 4.1    |

为了研究功函数对 FinFET SRAM 翻转阈值 的影响,同时验证栅氧厚度影响 SRAM 翻转阈 值的机理,进行了功函数与 SRAM 单粒子翻转 阈值的仿真。在进行仿真的过程中,每一次仿 真仅对 NMOS 或 PMOS 中的一种晶体管的功函 数进行波动调整,以研究同一种晶体管的工艺 波动对 SRAM 翻转阈值的影响。仿真的结果见 表 6。仿真结果显示,对于 NMOS 晶体管而言, 功函数的升高使得 SRAM 翻转阈值升高,反之 下降;对于 PMOS 晶体管而言,功函数升高使得 SRAM 翻转阈值下降,反之升高。由于 NMOS 和 PMOS 晶体管的载流子分别为电子和空穴,对于 NMOS 晶体管而言,功函数升高意味着晶体管阈 值电压升高、饱和电流降低、晶体管开关速度降 低;对于PMOS晶体管而言,功函数升高意味着 晶体管阈值电压降低、饱和电流升高、晶体管开 关速度提高。在体硅的研究中表明,更慢的晶 体管开关速度意味着更低的单粒子瞬态脉冲和 更高的翻转阈值[2],功函数的仿真结果与体硅中 的相关研究保持了一致。此外,仿真结果显示,相 较于 PMOS, NMOS 对单粒子翻转阈值的影响更为 显著。虽然功函数对 FinFET 工艺下的翻转阈值 产生了影响,然而相较于体硅工艺,其波动仍然 微小。

#### 表 6 不同晶体管功函数下的翻转阈值

Tab. 6 The upset threshold under work function variation 单位·MeV·cm²/mg

| 工艺参数     | SS 工艺角 | TT 工艺角 | FF 工艺角 |

|----------|--------|--------|--------|

| NMOS 功函数 | 4. 1   | 4.0    | 3.9    |

| PMOS 功函数 | 4.0    | 4.0    | 3.9    |

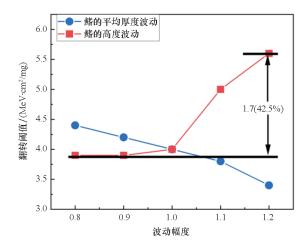

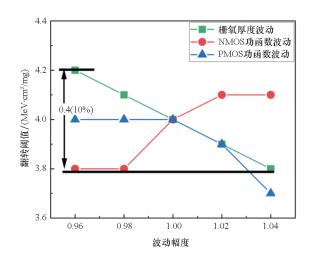

为了进一步探究 FinFET SRAM 工艺涨落对 单粒子翻转阈值波动影响相较平面工艺较小的原 因,按照文献[4]中描述的体硅条件下关键工艺 参数的波动范围,对 FinFET SRAM 的单粒子翻转 阈值进行了仿真。其相关参数波动范围见表 7。 除表7中提及的参数发生了变化外,其他仿真设 置不变。仿真结果见图 8 和图 9。仿真结果显 示,在波动幅度为±20%的鳍的平均厚度和鳍的 高度仿真中,鳍的高度波动造成的单粒子翻转阈 值波动幅度最大, 阈值波动绝对值为 1.7 MeV· cm²/mg, 与标准翻转阈值相比波动范围达 42.5%;在波动幅度为±4%的栅氧厚度、NMOS 和 PMOS 功函数仿真中, 栅氧厚度波动造成的单 粒子翻转阈值波动幅度最大,阈值波动绝对值为 0.4 MeV·cm<sup>2</sup>/mg,与标准翻转阈值相比波动范 围为10.0%。相较于平面工艺,从仿真结果可以 得出 FinFET 器件工艺涨落对单粒子翻转阈值波 动影响较小的原因。其一,FinFET 工艺的电荷收 集更多发生在鳍上,其收集量取决于沉积量[33], 与平面工艺相比,鳍上电荷沉积量远少于体上沉 积的量,而工艺波动难以导致鳍上电荷的沉积量 发生大的改变,鳍平均高度和厚度的波动引发翻 转阈值波动大于栅氧和功函数的波动的仿真结果 有效支持了这一结论;其二,与平面工艺 ±20%的 参数波动相比, FinFET 器件最高仅为 2% 的参数 波动,其波动幅度远小于平面工艺。综上所述,对

### 表 7 鳍的厚度、鳍的高度、栅氧厚度和 功函数在体硅工艺波动条件下的波动范围

Tab. 7 The fin thickness, fin height, oxide thickness and work function range at bulk planar fluctuation condition

| 工艺参数     | 基准参数                | 波动范围             | 波动幅度/% |

|----------|---------------------|------------------|--------|

| 鳍的平均厚度   | 9.3 nm              | 7.44 ~11.16 nm   | ± 20   |

| 鳍的高度     | 45.0 nm             | 36 ~54 nm        | ± 20   |

| 栅氧厚度     | 1.58 nm             | 1.517 ~ 1.643 nm | ±4     |

| NMOS 功函数 | $4.626~\mathrm{eV}$ | 4.441 ~4.811 eV  | ±4     |

| PMOS 功函数 | 4.660 eV            | 4.474 ~4.846 eV  | ±4     |

图 8 鳍的平均厚度和鳍的高度在平面体硅工艺波动 条件下的 SRAM 单粒子翻转阈值

Fig. 8 The upset threshold under fin average thickness and height at bulk planar process fluctuation condition

图 9 栅氧厚度、NMOS 和 PMOS 功函数在平面体 硅工艺波动条件下的 SRAM 单粒子翻转阈值 Fig. 9 The upset threshold under oxide thickness, NMOS and PMOS work function at bulk planar process fluctuation condition

于 FinFET SRAM 器件在平面工艺的波动范围下,鳍的高度波动造成了最大的单粒子翻转阈值波动,但得益于鳍上沉积电荷量少和更稳定的工艺控制,相较平面工艺, FinFET SRAM 工艺涨落对单粒子翻转阈值波动影响较小。

#### 4 结论

本文研究了亚 20 nm FinFET 工艺下典型的单端口 SRAM 存储器单粒子翻转阈值随工艺涨落的变化。研究结果表明,亚 20 nm FinFET 工艺涨落对 SRAM 的翻转阈值产生的影响极其微小,其敏感节点位于与节点 Q 连接的 NMOS 晶体管漏极,这与体硅的研究结果明显不同。为了研究

FinFET 工艺涨落对 SRAM 存储器单粒子翻转阈值的影响,提出了一套基于某商用工艺的 SRAM 三维 TCAD 模型的建模方法,建立的三维 TCAD 模型具有较高的精度,其关键电学特性误差均小于 10%。基于该模型研究了具体的工艺涨落因素对 FinFET SRAM 单粒子翻转阈值的影响。仿真结果表明,功函数和栅氧厚度对翻转阈值产生了影响,但产生的影响并不显著,这与平面工艺完全不同。将波动范围按照平面工艺放大,发现鳍的高度波动的影响最大,得益于 FinFET 工艺下鳍上沉积电荷量少和更稳定的工艺控制, FinFET SRAM 单粒子翻转阈值波动显著小于平面工艺。

本研究结果指出,相较于传统的平面体硅工艺,FinFET 器件工艺波动对 SRAM 存储器的翻转阈值未产生显著影响,其具有更好的工艺稳定性。该发现意味着基于亚 20 nm FinFET 工艺设计的抗辐射集成电路在考虑对 SRAM 加固时,可以不必考虑工艺波动造成的额外加固开销,对研制高一致性的抗辐射宇航用集成电路具有重要意义。

## 参考文献(References)

- [1] 张坤. FinFET 工艺涨落分析及其对相关电路的影响研究[D]. 北京: 清华大学, 2018.

ZHANG S. Analysis of FinFET fluctuation and research on relevant circuit [D]. Beijing: Tsinghua University, 2018.

(in Chinese)

- [2] KAUPPILA A V, BHUVA B L, KAUPPILA J S, et al. Impact of process variations on SRAM single event upsets[J]. IEEE Transactions on Nuclear Science, 2011, 58(3): 834 – 839

- [3] ROYER P, GARCÍA-REDONDO F, LÓPEZ-VALLEJO M. Evolution of radiation-induced soft errors in FinFET SRAMs under process variations beyond 22nm [C]//Proceedings of the 2015 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH'15), 2015; 112 – 117.

- [4] WANG T Q, XIAO L Y, ZHOU B, et al. Analysis of process variations impact on the single-event transient quenching in 65 nm CMOS combinational circuits [J]. Science China Technological Sciences, 2014, 57(2): 322-331.

- [5] OLOWOGEMO S A, QIU H, LIN B T, et al. Model-based analysis of single-event upset (SEU) vulnerability of 6T SRAM using FinFET technologies [C]//Proceedings of the 2022 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2022: 1-4.

- [6] KUMAR S, CHO M, EVERSON L R, et al. A back-sampling chain technique for accelerated detection, characterization, and reconstruction of radiation-induced transient pulses[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2021, 29(12): 2086 2097.

- [7] DE MELO HANG M E, MARQUES C M, BUTZEN P F, et al. Soft error sensibility window at FinFET DICE SRAM[C]//Proceedings of the 2021 IEEE 12th Latin America Symposium on Circuits and System (LASCAS),

- 2021:1-4.

- [8] D'AMICO J V, BALL D R, CAO J C, et al. Single-event upsets in a 7-nm bulk FinFET technology with analysis of threshold voltage dependence [J]. IEEE Transactions on Nuclear Science, 2021, 68(5): 823-829.

- [9] XU L, CAO J, BHUVA B L, et al. Single-event upset responses of dual- and triple-well D flip-flop designs in 7-nm bulk FinFET technology [C]//Proceedings of the IEEE International Reliability Physics Symposium (IRPS), 2019: 1-5.

- [10] PETROSYANTS K O, SILKIN D S, POPOV D A, et al. Analysis of SEU effects in MOSFET and FinFET based 6T SRAM cells [C]//Proceedings of the Moscow Workshop on Electronic and Networking Technologies (MWENT), 2022: 1-4.

- [11] CHI Y Q, HUANG P C, SUN Q, et al. Characterization of single-event upsets induced by high-LET heavy ions in 16-nm bulk FinFET SRAMs [J]. IEEE Transactions on Nuclear Science, 2022, 69(5): 1176-1181.

- [12] VIBHU V, MITTAL S, KUMAR V. Machine learning-based model for single event upset current prediction in 14 nm FinFETs[C]// Proceedings of the 36th International Conference on VLSI Design and 2023 22nd International Conference on Embedded Systems (VLSID), 2023: 1-6.

- [13] COPETTI T, CARDOSO MEDEIROS G, TAOUIL M, et al. Evaluation of single event upset susceptibility of FinFET-based SRAMs with weak resistive defects[J]. Journal of Electronic Testing, 2021, 37(3): 383 394.

- [14] LI D Q, LIU T Q, ZHAO P X, et al. Strategy to mitigate single event upset in 14-nm CMOS bulk FinFET technology[J]. Chinese Physics B, 2022, 31(5): 056106.

- [15] AGARWAL H, GUPTA C, CHANG H L, et al. BSIM-BULK106. 2. 0 MOSFET compact model: technical manual [M]. Berkeley: BSIM GROUP, 2017.

- [16] NAINANI A, GUPTA S, MOROZ V, et al. Is strain engineering scalable in FinFET era? Teaching the old dog some new tricks [C]//Proceedings of the International Electron Devices Meeting, 2012; 18.3.1-18.3.4.

- [17] JAMES D. Moore's law continues into the 1x-nm era[C]// Proceedings of the 27th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), 2016: 324-329.

- [18] NIIMI H, LIU Z G, GLUSCHENKOV O, et al. Sub-10  $^{-9}\Omega$ -cm<sup>2</sup> n-type contact resistivity for FinFET technology [J]. IEEE Electron Device Letters, 2016, 37(11): 1371 1374.

- [19] CHANG C Y, KHAJA F A, HOLLAR K E, et al. Ultra-low  $(1.2\times10^{-9}~\Omega\cdot\text{cm}^2)~\text{p-Si}_{0.55}\text{Ge}_{0.45}\text{contact resistivity}~(\rho_c)$  using nanosecond laser anneal for 7 nm nodes and beyond[C]// Proceedings of the 2017–17th International Workshop on Junction Technology (1WJT), 2017: 23 26.

- [20] YANG C H, CHEN S C, TSAI Y S, et al. The physical explanation of TDDB power law lifetime model through oxygen vacancy trap investigations in HKMG NMOS FinFET devices[C]// Proceedings of the IEEE International Reliability Physics Symposium (IRPS), 2017: 3C - 4.1 -3C - 4.6.

- [21] AUTH C, ALLEN C, BLATTNER A, et al. A 22 nm high performance and low-power CMOS technology featuring fully-

- depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors [ C ]//Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), 2012: 131 132.

- [22] NATARAJAN S, AGOSTINELLI M, AKBAR S, et al. A 14 nm logic technology featuring 2nd-generation FinFET, airgapped interconnects, self-aligned double patterning and a 0.058 8 μm² SRAM cell size [C]//Proceedings of the 2014 IEEE International Electron Devices Meeting, 2014: 3.7.1 3.7.3.

- [23] WUSY, LINCY, CHIANGMC, et al. A 16 nm FinFET CMOS technology for mobile SoC and computing applications [C]// Proceedings of the IEEE International Electron Devices Meeting, 2013: 9.1.1-9.1.4.

- [24] WU S Y, LIN C Y, CHIANG M C, et al. An enhanced 16 nm CMOS technology featuring 2nd generation FinFET transistors and advanced Cu/low-k interconnect for low power and high performance applications [C]//Proceedings of the IEEE International Electron Devices Meeting, 2014; 3.1.1 3.1.4.

- [25] HUANG T, LI R L, CAI H L, et al. Suppression of threshold voltage variation by TiN surface treatment for N-FinFETs with very thin work function metal layers [J]. IEEE Transactions on Electron Devices, 2023, 70(4): 1554-1559.

- [26] VAN MEER H, VARIAM N. Recent advances in contact resistance improvement in advanced logic [C]//Proceedings of the 20th International Workshop on Junction Technology (IWJT), 2021: 1-4.

- [27] JIANG L, GUI Y, SHEN Y T. Titanium silicide anneal process research for 14 nm FinFET technology [ C ]//

Proceedings of the China Semiconductor Technology International Conference (CSTIC), 2020; 1-3.

- [28] RAINE M, GAILLARDIN M, SAUVESTRE J E, et al. Effect of the ion mass and energy on the response of 70-nm SOI transistors to the ion deposited charge by direct ionization [C]//Proceedings of the European Conference on Radiation and Its Effects on Components and Systems, 2009: 521-528.

- [29] AHLBIN J R, GADLAGE M J, BALL D R, et al. The effect of layout topology on single-event transient pulse quenching in a 65 nm bulk CMOS process [J]. IEEE Transactions on Nuclear Science, 2010, 57(6): 3380-3385.

- [30] LIU J T, XU X Y, SUN Q, et al. Pulse quenching based radiation-hardened by design technique for analog single-event transient mitigation on an operational amplifier in 28 nm bulk CMOS process[J]. Semiconductor Science and Technology, 2020, 35(7): 075026.

- [31] LI H C, XIAO L Y, LI J, et al. Mitigation technique for single event transient via pulse quenching [ J ]. IEEE Transactions on Device and Materials Reliability, 2021, 21(3): 405-415.

- [32] TAKEUCHI K, SAKAMOTO K, YUKUMATSU K, et al. Characteristic charge collection mechanism observed in FinFET SRAM cells [J]. IEEE Transactions on Nuclear Science, 2022, 69(8): 1833-1839.

- [33] NSENGIYUMVA P, MASSENGILL L W, ALLES M L, et al. Analysis of bulk FinFET structural effects on single-event cross sections [J]. IEEE Transactions on Nuclear Science, 2017, 64(1): 441-448.